## **XFP 10G Dual LC Optical Transceivers**

### INTRODUCTION

This design guide provides the information needed to incorporate OptixCom's fiber optics transceiver products in the customer's system. The XFP series of transceiver products are compliant with the XFP mutli-source agreement (MSA) INF-8077i (Rev. 4.5, 2005) and IEEE 802.3 Section 4 on "52. Physical Medium Dependent (PMD) sublayer and baseband medium, type 10GBASE-S (short wavelength serial), 10GBASE-L (long wavelength serial), and 10GBASE-E (extra long wavelength serial)". For more detail information, please refer to the URL <a href="http://www.xfpmsa.org">http://www.xfpmsa.org</a> or visit OptixCom web site: <a href="http://www.OptixCom.com">http://www.OptixCom.com</a> for the official documentation.

The reference guide covers the following topics:

- A. PIN ASSIGNMENT & DESCRIPTION

- **B. RECOMMENDED INTERFACE CIRCUIT**

- C. PACKAGE OUTLINE

- D. SFP TRANSCEIVER HOST BOARD MECHANICAL LAYOUT

- E. ELECTRICAL CONNECTOR MECHANICAL LAYOUT

- F. CONNECTOR INSERTION, EXTRACTION, AND RETENTION FORCE

- **G. TIMING REQUIREMENTS**

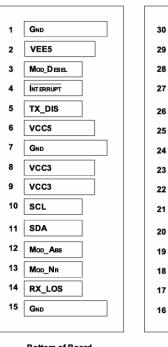

#### A. PIN ASSIGNMENT & DESCRIPTION

The XFP transceiver contains a printed circuit board that mates with the electrical connector. The pads are designed for a sequenced mating in the following order: ground contacts, power contacts, and signal contacts.

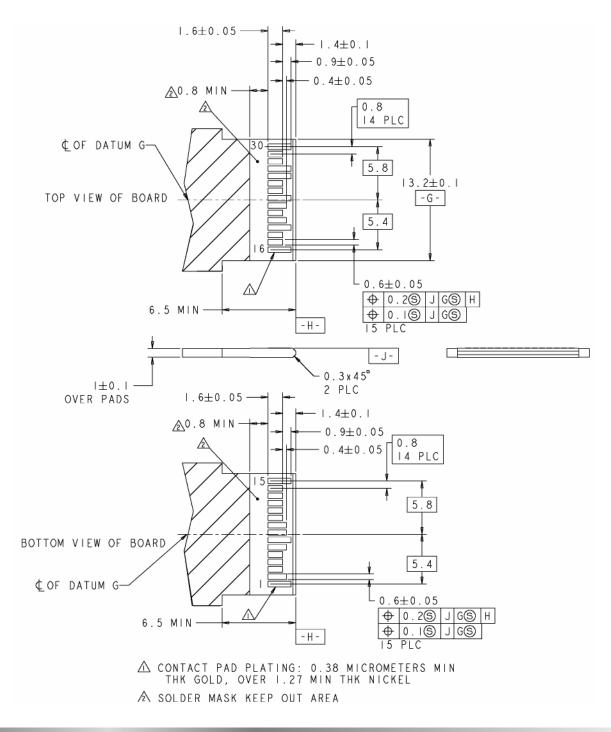

#### **Host Board Connector Pad Layout**

### XFP Transceiver Pad Layout

Bottom of Board (As viewed thru top of board) 30 GND

29 TD+

28 TD27 GND

26 GND

25 REFCLK24 REFCLK+

23 GND

22 VCC2

21 P\_Down/RST

20 VCC2

19 GND

18 RD+

17 RD16 GND

Top of Board

U.S.A. Office: Optix Communications, Inc.

17901 Von Karman Avenue, Suite 600, Irvine, CA 92614 Tel: (949) 679-5712 Fax: (949) 420-2134 http://www.OptixCom.com http://www.OpticalTransceiver.com Email: Support@OptixCom.com Germany Office: OptixCom GmbH

Magdeburger Strasse 18, 66121 Saarbruecken, Germany Tel: +49 (0)681 4013-5172

| Pin | Logic     | Symbol    | Name/Description                                                                                           | Note                                                                                                                                                      |                                                                                                                                      |

|-----|-----------|-----------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1   |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

| 2   |           | VEE5      | Optional -5.2V Power Supply                                                                                |                                                                                                                                                           |                                                                                                                                      |

| 3   | LVTTL-I   | Mod_DeSel | Module De-select; When held low allows module to respond to 2-wire serial interface                        |                                                                                                                                                           |                                                                                                                                      |

| 4   | LVTTL-O   | Interrupt | Interrupt; Indicates presence of an important condition which can be read over the 2-wire serial interface | 2                                                                                                                                                         |                                                                                                                                      |

| 5   | LVTTL-I   | TX_DIS    | Transmitter Disable; Turns off transmitter laser output                                                    |                                                                                                                                                           |                                                                                                                                      |

| 6   |           | VCC5      | +5V Power Supply                                                                                           |                                                                                                                                                           |                                                                                                                                      |

| 7   |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

| 8   |           | VCC3      | +3.3V Power Supply                                                                                         |                                                                                                                                                           |                                                                                                                                      |

| 9   |           | VCC3      | +3.3V Power Supply                                                                                         |                                                                                                                                                           |                                                                                                                                      |

| 10  | LVTTL-I/O | SCL       | 2-Wire Serial Interface Clock                                                                              | 2                                                                                                                                                         |                                                                                                                                      |

| 11  | LVTTL-I/O | SDA       | 2-Wire Serial Interface Data Line                                                                          | 2                                                                                                                                                         |                                                                                                                                      |

| 12  | LVTTL-O   | Mod_Abs   | Indicates Module is not present. Grounded in the Module                                                    | 2                                                                                                                                                         |                                                                                                                                      |

| 13  | LVTTL-O   | Mod_NR    | Module Not Ready; Indicating Module Operational Fault                                                      | 2                                                                                                                                                         |                                                                                                                                      |

| 14  | LVTTL-O   | RX_LOS    | Receiver Loss Of Signal Indicator                                                                          | 2                                                                                                                                                         |                                                                                                                                      |

| 15  |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

| 16  |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

| 17  | CML-O     | RD-       | Receiver Inverted Data Output                                                                              |                                                                                                                                                           |                                                                                                                                      |

| 18  | CML-O     | RD+       | Receiver Non-Inverted Data Output                                                                          |                                                                                                                                                           |                                                                                                                                      |

| 19  |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

| 20  |           | VCC2      | +1.8V Power Supply                                                                                         | 3                                                                                                                                                         |                                                                                                                                      |

| 21  | LVTTL-I   | LVTTL-I   | P Down/RST                                                                                                 | Power down; When high, requires the module to limit power consumption to 1.5W or below. 2-Wire serial interface must be functional in the low power mode. |                                                                                                                                      |

|     |           |           |                                                                                                            |                                                                                                                                                           | Reset; The falling edge initiates a complete reset of the module including the 2-wire serial interface, equivalent to a power cycle. |

| 22  |           | VCC2      | +1.8V Power Supply                                                                                         | 3                                                                                                                                                         |                                                                                                                                      |

| 23  |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

| 24  | PECL-I    | RefCLK+   | Reference Clock Non-Inverted Input, AC coupled on the host board                                           |                                                                                                                                                           |                                                                                                                                      |

| 25  | PECL-I    | RefCLK-   | Reference Clock Inverted Input, AC coupled on the host board                                               |                                                                                                                                                           |                                                                                                                                      |

| 26  |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

| 27  |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

| 28  | CML-I     | TD-       | Transmitter Inverted Data Input                                                                            |                                                                                                                                                           |                                                                                                                                      |

| 29  | CML-I     | TD+       | Transmitter Non-Inverted Data Input                                                                        |                                                                                                                                                           |                                                                                                                                      |

| 30  |           | GND       | Module Ground                                                                                              | 1                                                                                                                                                         |                                                                                                                                      |

- 1. Module ground pins Gnd are isolated from the module case and chassis ground within the module.

- 2. Shall be pulled up with 4.7K-10Kohms to a voltage between 3.15V and 3.45V on the host board.

- 3. The 1.8 V power supply can be optionally programmed to voltages lower than 1.8 V in modules supporting the variable power supply.

Tel: (949) 679-5712 Fax: (949) 420-2134

#### LOW SPEED ELECTRICAL HARDWARE PINS

In addition to the 2-wire serial interface the XFP module has the following low speed pins for control and status:

Mod\_NR Mod\_DeSel Interrupt TX\_DIS

Mod\_ABS RX\_LOS P\_Down/RST.

#### MOD\_NR

The Mod\_NR is an output pin that when High, indicates that the module has detected a condition that renders transmitter and or receiver data invalid, shall consist of logical OR of the following signals:

- Transmit Signal Conditioner Loss of Lock

- Transmitter Laser Fault

- Receiver Signal Conditioner Loss of Lock

Other conditions deemed valuable to the detection of fault may be added to the Mod\_NR. The Mod\_NR output pin is an open collector and must be pulled to Host\_Vcc on the host board.

#### MOD\_DESEL

The Mod\_DeSel is an input pin. When held Low by the host, the module responds to 2-wire serial communication commands. The Mod\_DeSel allows the use of multiple XFP modules on a single 2-wire interface bus. When the Mod\_DeSel pin is "High", the module shall not respond to or acknowledge any 2-wire interface communication from the host. Mod\_DeSel pin must be pulled to VCC3 in the module.

In order to avoid conflicts, the host system shall not attempt 2-wire interface communications within the Mod\_DeSel assert time after any XFP modules are deselected. Similarly, the host must wait at least for the period of the Mod\_DeSel deassert time before communicating with the newly selected module. The assertion and deassertion periods of different modules may overlap as long as the above timing requirements are met.

#### **INTERRUPT**

Interrupt is an output pin. When "Low", indicates possible module operational fault or a status critical to the host system. The Interrupt pin is an open collector output and must be pulled up to Host\_Vcc the host board.

#### TX\_DIS

TX\_DIS is an input pin. When TX\_DIS is asserted High, the XFP module transmitter output must be turned off. The TX\_DIS pin must be pulled up to VCC3 in the XFP module.

#### MOD ABS

Mod\_ABS is pulled up to Host\_Vcc on the host board and grounded in the XFP module. Mod\_ABS is then asserted "High" when the XFP module is physically absent from a host slot.

#### RX\_LOS

The RX\_LOS when High indicates insufficient optical power for reliable signal reception. The RX\_LOS pin is an open collector output and must be pulled up to Host\_Vcc on the host board.

Germany Office: OptixCom GmbH

#### P DOWN/RST

This is a multifunction pin for module Power Down and Reset. The P\_Down/RST pin must be pulled up to VCC3 in the XFP module.

#### POWER DOWN FUNCTION

The P\_Down pin, when held High by the host, places the module in the standby (Low Power) mode with a maximum power dissipation of 1.5W. This protects hosts which are not capable of cooling higher power modules which may be accidentally inserted.

The module's 2-wire serial interface and all laser safety functions must be fully functional in this low power mode. During P\_Down, the module shall still support the completion of reset Interrupt, as well as maintain functionality of the variable power supply.

#### **RESET FUNCTION**

The negative edge of P\_Down/RST signal initiates a complete module reset.

#### MODULE BEHAVIOR DURING POWER DOWN AND RESET

During execution of a reset (t\_init) or while held in Power Down mode, a module may be unable to determine the correct value for Mod\_NR and RX\_LOS. These outputs as well as all interrupt related flags, except completion of Reset flag, shall be disregarded by the host. When the module completes a Reset and is not in Power Down mode, the module must represent the correct value of both signals on its outputs before posting a completion of reset interrupt to the host.

At no time shall a module cause spurious assertion of the Interrupt pin.

When a host initially applies power to a module with the P\_Down/RST signal asserted, a module comes up in power down mode. The module shall only assert the Interrupt signal pin to inform the host it has completed a reset. The completion of reset flag shall be the only interrupt source flag set during power down mode. The host is expected to clear this interrupt before releasing the module from the power down mode. The transition from power down mode to normal mode will trigger a reset of the module and result in a 2nd module reset and a 2nd reset completion interrupt to the host

Tel: (949) 679-5712 Fax: (949) 420-2134

#### LOW SPEED ELECTRICAL SPECIFICATIONS

Low speed signaling is based on Low Voltage TTL (LVTTL) operating at Vcc3 at a nominal supply of (3.3V± 5%). Hosts shall use a pull-up resistor connected to a host Vcc of +3.3 volts (3.15 to 3.45 volts) on the 2-wire interface SCL (clock), SDA (Data), and all low speed status outputs.

The XFP low speed electrical specifications are given in the following. This specification ensures compatibility between host bus masters and XFP SCL/SDA lines and compatibility with I<sup>2</sup>C.

#### LOW SPEED CONTROL AND SENSE SIGNALS, ELECTRONIC CHARACTERISTICS

| Parameter                                     | Symbol | Min.           | Max.           | Unit | Conditions                                                                                    |

|-----------------------------------------------|--------|----------------|----------------|------|-----------------------------------------------------------------------------------------------|

| XFP Interrupt, Mod_NR,                        | Vol    | 0.0            | 0.40           | ٧    | Rpullup pulled to host_Vcc, measured at host side of connector. lo.(max) = 3 mA               |

| RX_LOS                                        | Vон    | host_Vcc - 0.5 | host_Vcc + 0.3 | ٧    | Rpullup pulled to host_Vcc, measured at host side of connector.                               |

| XFP TX_Dis,                                   | VIL    | -0.3           | 0.8            | ٧    | Rpullup pulled to VCC3,measured at XFP side of connector. In(max) = -10 uA                    |

| P_Down/RST                                    | VIH    | 2.0            | VCC3+0.3       | ٧    | Rpullup pulled to VCC3, measured at XFP side of connector. IH(max) = 10 uA                    |

|                                               | Vol    | 0.0            | 0.40           | ٧    | Rpullup <sup>1</sup> pulled to host_Vcc, measured at host side of connector. lo.(max) = 3 mA  |

| XFP SCL and SDA                               | Vон    | host_Vcc - 0.5 | host_Vcc + 0.3 | ٧    | Rpullup <sup>1</sup> pulled to host_Vcc, measured at host side of connector.                  |

|                                               | VIL    | -0.3           | Vcc3*0.3       | ٧    | Rpullup <sup>1</sup> pulled to Host_VCC, measured at XFP side of connector. II.(max) = -10 uA |

| XFP SCL and SDA                               | VIH    | Vcc3*0.7       | VCC3 + 0.5     | ٧    | Rpullup <sup>1</sup> pulled to Host_VCC, measured at XFP side of connector. In(max) = 10 uA   |

| Leakage Current                               | lı     | -10            | 10             | μΑ   |                                                                                               |

| Capacitance for<br>XFP SCL and<br>SDA I/O Pin | Ci     |                | 14             | рF   | 10pF for XFP IC I/O pin, 4 pF<br>for XFP PCB trace                                            |

| Total bus capacitive                          |        |                | 100            | рF   | At 400 KHz, 3.0 Kohms Rp, max<br>At 100 KHz, 8.0 Kohms Rp, max                                |

| load for SCL<br>and for SDA                   | Сь     |                | 400            | рF   | At 400 KHz, 0.80 Kohms Rp, max At<br>100 KHz, 2.0 Kohms Rp, max                               |

<sup>1.</sup> For combinations of Rpullup (Rp), bus capacitance and speed, see Philips I<sup>2</sup>C specification revision 2.1, figures 39 and 44. Rise and fall time measurement levels are defined in the XFP management interface ac electrical specifications. Active bus termination may be used by the host in place of a pullup resistor, as described in the Philips I2C specification

Saarbruecken, Germany Tel: +49 (0)681 4013-5172

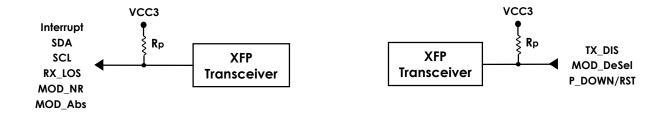

#### **B. RECOMMENDED INTERFACE CIRCUIT**

### **OptixCom XFP Transceiver** + dt ▶−Œ CML 100 Ω Lines Laser **Driver** TX\_DIS MOD Abs 11 SDA Interrupt 24 ◀ RefCLK + **EEPROM** CML 100 Ω Lines MOD\_NR 25 ■ RefCLK – 21 P\_Down/RST 10 SCL MOD DeSel RX\_LOS TIA & 17 **Post Amp** 100 Ω Lines

All the LVTTL interface logic pins are open collector compatible. A pull up resistor  $R_P$  is used in the following scheme. The value of  $R_P$  is between 4.7K $\Omega$  to 10K  $\Omega$ .

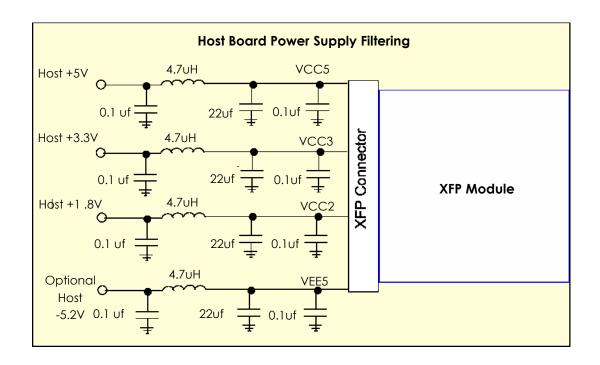

The XFP host has 3 power supplies +1.8 V, +3.3 V, +5.0 V and an optional -5.2 V supply. The +1.8 V and +3.3 V supplies have two designated power pins in the connector for each power supply rail. The +5 V and -5.2 supplies have one designated power pin each. The maximum continuous or peak current carrying capacity for each connector pin is 500 mA.

The host system may alter the VCC2 supply to a voltage level lower that the nominal +1.8 V value. This mode of operation is optional and can be supported by modules and hosts that strive to meet lower power/current requirements. Modules supporting this optional lower power mode must be backwards compatible with modules and hosts supporting only 1.8 V on VCC2, i.e. modules implementing these optional modes must be able to operate normally with a voltage of +1.8 V applied on their VCC2 pins (albeit with higher power dissipation). XFP module maximum power dissipation must meet one of the following classes:

Power Level 1 modules – Up to 1.5 W Power Level 2 modules – Up to 2.5 W

Power Level 3 modules - Up to 3.5 W

Power Level 4 modules – Greater than 3.5 W

To avoid exceeding system power supply limits and cooling capacity, the module may be placed in the power down mode by pulling pin 21 High. This guarantees module operating in Low Power mode with maximum power dissipation of  $\leq 1.5$ W.

A host board together with XFP module(s) forms an integrated power system. The host supplies stable power to the module. The module limits electrical noise coupled back into the host and limits inrush charge/current during hot plug insertion.

The example host board power supply filtering shown below will meet the noise filtering requirements in most systems. Other filtering implementations or local regulation may be used to meet the power noise output requirements described in Section 2.7.1 of XFP MSA document.

Any voltage drop across a filter network on the host is counted against the Host DC set point accuracy specification in Table 4 of XFP MSA. For this reason, the example filter may not be appropriate for a host powering multiple XFPs and/or other host components from a shared voltage supply.

Irvine, CA 92614

Tel: (949) 679-5712 Fax: (949) 420-2134

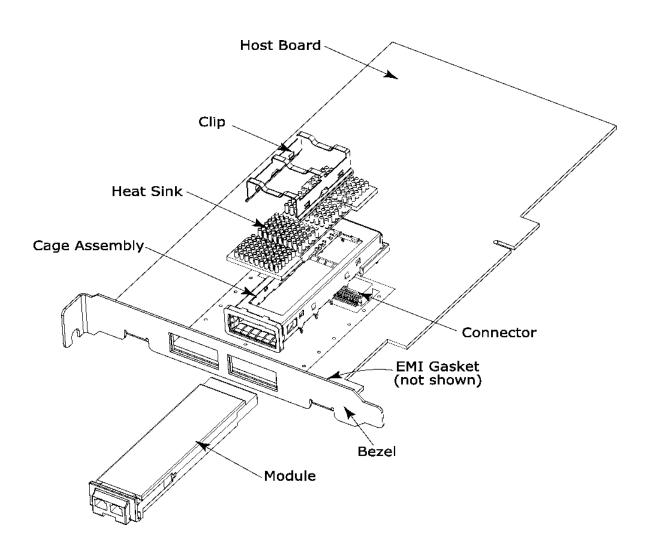

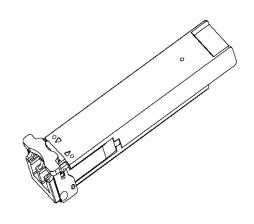

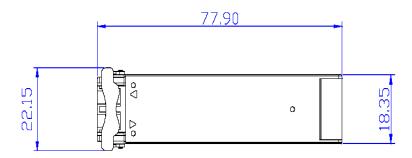

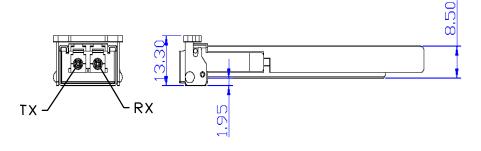

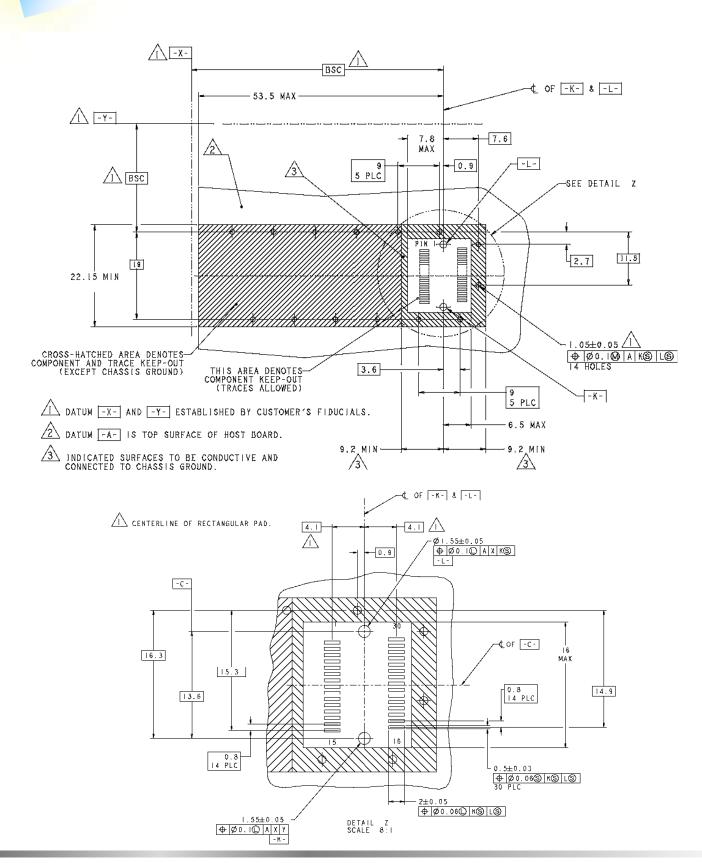

#### C. PACKAGE OUTLINE

The mechanical components defined in this section are illustrated in the following. The module, clip and connector dimensions are constant for all applications. While the bezel, cage assembly, EMI gasket and heat sink can be designed and/or adjusted for the individual application. The relatively small form factor of the XFP module combined with an adaptable heatsink option allows host system design optimization of module location, heat sink shape/dimension/fins design, and airflow control. The module can be inserted and removed from the cage with the heat sink and clip attached. Please note that OptixCom only offers the XFP transceiver module but not other components. Refer to XFP MSA document for more details of the other components.

### **XFP Mechanical Components**

### **Mechanical Outline Dimensions**

Unit: mm, typical tolerance for these dimensions is  $\pm$  0.2 mm

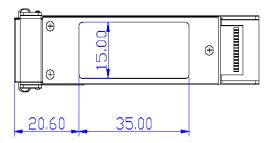

#### D. XFP TRANSCEIVER HOST BOARD MECHANICAL LAYOUT

The design of the mating portion of the transceiver printed circuit board and the electrical pad layout is illustrated in the following. The recommended contact pad plating for the printed circuit board is 0.38 micrometers minimum gold over 1.27 micrometers minimum thick nickel.

17901 Von Karman Avenue, Suite 600, Irvine, CA 92614 Tel: (949) 679-5712 Fax: (949) 420-2134 http://www.OptixCom.com http://www.OpticalTransceiver.com Email: Support@OptixCom.com

Magdeburger Strasse 18, 66121 Saarbruecken, Germany Tel: +49 (0)681 4013-5172

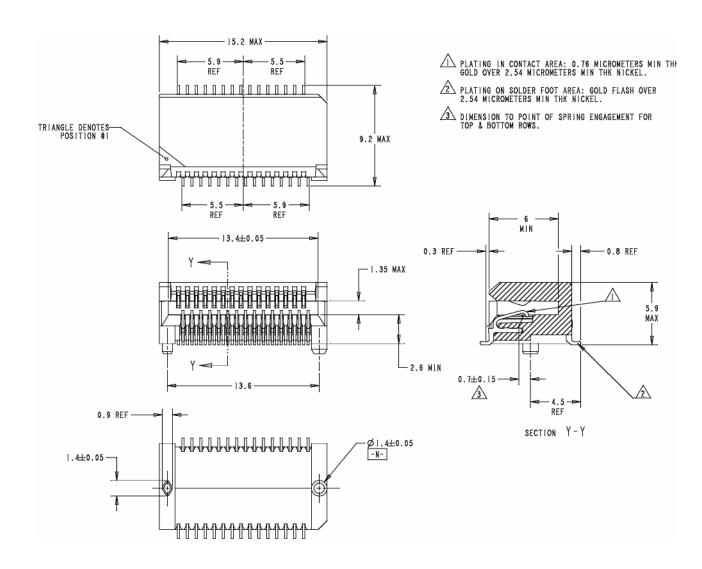

#### E. ELECTRICAL CONNECTOR MECHANICAL LAYOUT

The XFP Connector is a 30-contact, right angle surface mount connector and available from several manufacturers1. An example connector such as 788862-2 manufactured by Tyco is shown in the following. Newer versions of this connector are available from Tyco, Molex, and Harting with improved electrical performance.

Page 12

### F. CONNECTOR INSERTION, EXTRACTION, AND RETENTION FORCE

The requirement for the various functional forces and the durability cycles are specified in the following Table.

| Measurement                                    | Minimum | Maximum | Units   | Comments                                                                |

|------------------------------------------------|---------|---------|---------|-------------------------------------------------------------------------|

| XFP transceiver insertion                      | 0       | 40      | Newtons |                                                                         |

| XFP transceiver extraction                     | 0       | 30      | Newtons |                                                                         |

| XFP transceiver retention                      | 90      | N/A     | Newtons | No damage to transceiver below 90N                                      |

| Cage retention (Latch strength)                | 180     | N/A     | Newtons | No damage to the latch below 180N                                       |

| Cage retention in Host Board                   | 133     | N/A     | Newtons | Force to be applied in a vertical direction with no damage to the cage. |

| Insertion / removal cycles,<br>connector/cage  | 100     | N/A     | cycles  |                                                                         |

| Insertion / removal cycles, XFP<br>Transceiver | 50      | N/A     | cycles  |                                                                         |

Tel: (949) 679-5712 Fax: (949) 420-2134

Saarbruecken, Germany Tel: +49 (0)681 4013-5172

### G. TIMING REQUIREMENTS OF CONTROL AND STATUS I/O

#### LOW SPEED ELECTRICAL HARDWARE PINS

The timing requirements of the control and status lines are listed in Table 3 of XFP MSA document. They are summarized in the Table below. The 2-wire serial bus timing is described in Chapter 4: XFP 2-Wire Interface Protocol in XFP MSA document.

### Timing Requirements of Control and Status I/0

| Parameter               | Symbol        | Min. | Max. | Unit | Conditions                                                                                 |

|-------------------------|---------------|------|------|------|--------------------------------------------------------------------------------------------|

| TX_DIS assert time      | t_off         |      | 10   | tsec | rising edge of TX_DIS to fall of output signal below 10% of nominal                        |

| TX_DIS negate time      | t_on          |      | 2    | msec | Falling edge of TX_DIS to rise of output signal above 90% of nominal                       |

| Time to initialize      | t_init        |      | 300  | msec | From power on or hot plug after supply meeting Table 4 or from falling edge of P_Down/RST. |

| Interrupt assert delay  | Interrupt_on  |      | 200  | msec | From occurrence of the condition triggering Interrupt                                      |

| Interrupt negate delay  | Interrupt_off |      | 500  | tsec | From clear on read Interrupt flags                                                         |

| P_Down/RST assert delay | P_Down/RST_on |      | 100  | tsec | From Power down initiation                                                                 |

| Mod_NR assert delay     | Mod_nr_on     |      | 1    | msec | From Occurrence of fault to assertion of MOD_NR                                            |

| Mod_NR negate delay     | Mod_nr_off    |      | 1    | msec | From clearance of signal to negation of MOD_NR                                             |

| P-Down reset time       |               | 10   |      | tsec | Min length of P-Down assert to initiate reset                                              |

| RX_LOS assert delay     | t_loss_on     |      | 100  | tsec | From Occurrence of loss of signal to assertion of RX_LOS                                   |

| RX_LOS negate delay     | t_loss_off    |      | 100  | tsec | From Occurrence of presence of signal to negation of RX_LOS                                |

Tel: (949) 679-5712 Fax: (949) 420-2134

Saarbruecken, Germany Tel: +49 (0)681 4013-5172

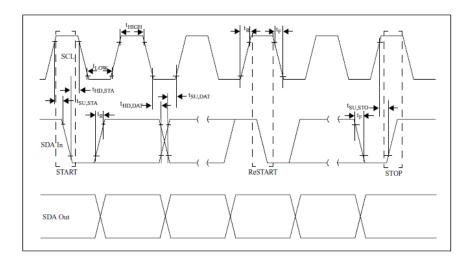

#### 2-WIRE TIMING DIAGRAM AND SPECIFICATIONS

XFP is positioned to leverage 2-wire timing (Fast Mode devices) to align the use of related cores on host ASICs. XFP 2-wire bus timing and AC specifications are shown in the following.

| Parameter                                         | Symbol                | Min. | Max. | Unit | Conditions                                                                                                            |

|---------------------------------------------------|-----------------------|------|------|------|-----------------------------------------------------------------------------------------------------------------------|

| Clock Frequency                                   | fscl                  | 0    | 400  | kHz  |                                                                                                                       |

| Clock Pulse Width Low                             | tLOW                  | 1.3  |      | μs   |                                                                                                                       |

| Clock Pulse Width High                            | tніGн                 | 0.6  |      | μs   |                                                                                                                       |

| Time bus free before new trans- mission can start | †BUF                  | 20   |      | μs   | Between STOP and START                                                                                                |

| START Hold Time                                   | †HD,STA               | 0.6  |      | μs   |                                                                                                                       |

| START Set-up Time                                 | tsu,sta               | 0.6  |      | μs   |                                                                                                                       |

| Data In Hold Time                                 | †HD,DAT               | 0    |      | μs   |                                                                                                                       |

| Data In Set-up Time                               | tsu,dat               | 0.1  |      | μs   |                                                                                                                       |

| Input Rise Time (100kHz)                          | †R,100                |      | 1000 | ns   | From (ML,MAX: 0.15) to (MH,MIN + 0.15)                                                                                |

| Input Rise Time (400kHz)                          | †R,400                |      | 300  | ns   | From (MLMAX- 0.15) to (MH,MIN + 0.15)                                                                                 |

| Input Fall Time (100kHz)                          | †F,100                |      | 300  | ns   | From (MH,MIN + 0.15) to (ML,MAX-0.15)                                                                                 |

| Input Fall Time (400kHz)                          | †F,400                |      | 300  | ns   | From (MH,MIN + 0.15) to (ML,MAX - 0.15)                                                                               |

| STOP Set-up Time                                  | tsu,sto               | 0.6  |      | μs   |                                                                                                                       |

| Host Supplied Module<br>DeSe-lect Setup Time      | Host_select_<br>setup | 2    |      | ms   | Setup time on the select lines before start of a host initiated serial bus sequence                                   |

| Host Supplied Module<br>DeSe-lect Hold Time       | Host_select_<br>hold  | 10   |      | μs   | Delay from completion of a serial bus sequence to changes of transceiver select status                                |

| Aborted sequence - bus release                    | Deselect_<br>Abort    |      | 2    | ms   | Delay from a host asserting Mod_DeSel<br>(at any point in a bus sequence), to the<br>XFP module releasing SCL and SDA |